#### UNIT III

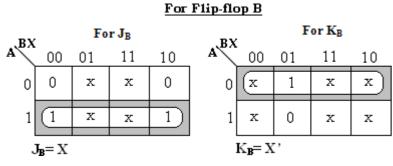

#### INTRODUCTION

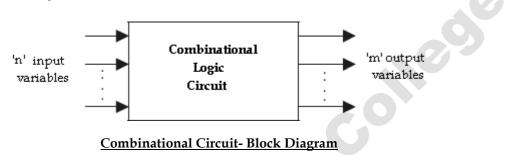

In *combinational logic circuits*, the outputs at any instant of time depend only on the input signals present at that time. For a change in input, the output occurs immediately.

In *sequential logic circuits*, it consists of combinational circuits to which storage elements are connected to form a feedback path. The storage elements are devices capable of storing binary information either 1 or 0.

The information stored in the memory elements at any given time defines the present state of the sequential circuit. The present state and the external circuit determine the output and the next state of sequential circuits.

Thus in sequential circuits, the output variables depend not only on the present input variables but also on the past history of input variables.

The rotary channel selected knob on an old-fashioned TV is like a combinational. Its output selects a channel based only on its current input – the position of the knob. The channel-up and channel-down push buttons on a TV is like a sequential circuit. The channel selection depends on the past sequence of up/down pushes.

The comparison between combinational and sequential circuits is given in table below.

| S.No | Combinational logic               | Sequential logic                     |  |

|------|-----------------------------------|--------------------------------------|--|

|      | The output variable, at all times | The output variable depends not only |  |

| 1    | depends on the combination of     | on the present input but also depend |  |

|      | input variables.                  | upon the past history of inputs.     |  |

| 2    | Memory unit is not required       | Memory unit is required to store the |  |

| 2    | Memory unit is not required       | past history of input variables.     |  |

| 3    | Faster in speed                   | Slower than combinational circuits.  |  |

| 4    | Easy to design                    | Comparatively harder to design.      |  |

| 5    | Eg. Parallel adder                | Eg. Serial adder                     |  |

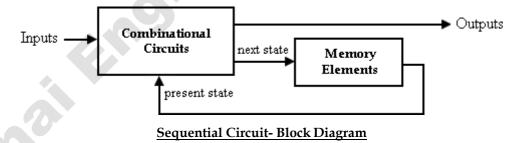

# 3.2 Classification of Logic Circuits

The sequential circuits can be classified depending on the timing of their signals:

- Synchronous sequential circuits

- Asynchronous sequential circuits.

In synchronous sequential circuits, signals can affect the memory elements only at discrete instants of time. In asynchronous sequential circuits change in input signals can affect memory element at any instant of time. The memory elements used in both circuits are Flip-Flops, which are capable of storing 1bit information.

| S.No | Synchronous sequential circuits                                                              | Asynchronous sequential circuits                                                        |  |  |

|------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--|--|

| 1    | Memory elements are clocked<br>Flip-Flops                                                    | Memory elements are either unclocked<br>Flip-Flops or time delay elements.              |  |  |

| 2    | The change in input signals can<br>affect memory element upon<br>activation of clock signal. | The change in input signals can affect<br>memory element at any instant of time.        |  |  |

| 3    | The maximum operating speed<br>of clock depends on time delays<br>involved.                  | Because of the absence of clock, it can<br>operate faster than synchronous<br>circuits. |  |  |

| 4    | Easier to design                                                                             | More difficult to design                                                                |  |  |

# <u>3.3</u> LATCHES:

Latches and Flip-Flops are the basic building blocks of the most sequential circuits. Latches are used for a sequential device that checks all of its inputs continuously and changes its outputs accordingly at any time independent of clocking signal. Enable signal is provided with the latch. When enable signal is active output changes occur as the input changes. But when enable signal is not activated input changes do not affect the output.

Flip-Flop is used for a sequential device that normally samples its inputs and changes its outputs only at times determined by clocking signal.

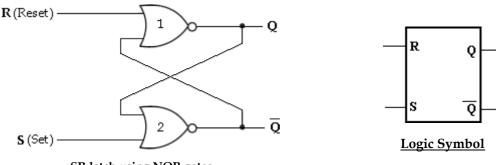

#### 3.3.1 SR Latch:

The simplest type of latch is the set-reset (SR) latch. It can be constructed from either two NOR gates or two NAND gates.

#### SR latch using NOR gates:

The two NOR gates are cross-coupled so that the output of NOR gate 1 is connected to one of the inputs of NOR gate 2 and vice versa. The latch has two outputs Q and Q' and two inputs, set and reset.

Before going to analyse the SR latch, we recall that a logic 1 at any input of a NOR gate forces its output to a logic 0. Let us understand the operation of this circuit for various input/ output possibilities.

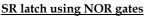

#### Case 1: S= 0 and R= 0

Initially, Q = 1 and Q' = 0

Let us assume that initially Q=1 and Q'=0. With Q'=0, both inputs to NOR gate 1 are at logic 0. So, its output, Q is at logic 1. With Q=1, one input of NOR gate 2 is at logic

1. Hence its output, Q' is at logic 0. This shows that when S and R both are low, the output does not change.

Initially, Q = 0 and Q' = 1

With Q'=1, one input of NOR gate 1 is at logic 1, hence its output, Q is at logic 0. With Q=0, both inputs to NOR gate 2 are at logic 0. So, its output Q' is at logic 1. In this case also there is no change in the output state.

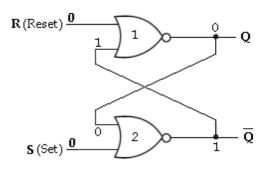

#### Case 2: S= 0 and R= 1

In this case, R input of the NOR gate 1 is at logic 1, hence its output, Q is at logic 0. Both inputs to NOR gate 2 are now at logic 0. So that its output, Q' is at logic 1.

#### Case 3: S= 1 and R= 0

In this case, S input of the NOR gate 2 is at logic 1, hence its output, Q is at logic 0. Both inputs to NOR gate 1 are now at logic 0. So that its output, Q is at logic 1.

#### Case 4: S= 1 and R= 1

When R and S both are at logic 1, they force the outputs of both NOR gates to the low state, i.e., (Q=0 and Q'=0). So, we call this an indeterminate or prohibited state, and represent this condition in the truth table as an asterisk (\*). This condition also violates the basic definition of a latch that requires Q to be complement of Q'. Thus in normal operation this condition must be avoided by making sure that 1's are not applied to both the inputs simultaneously.

We can summarize the operation of SR latch as follows:

- When S= 0 and R= 0, the output,  $Q_{n+1}$  remains in its present state,  $Q_n$ .

- When S= 0 and R= 1, the latch is reset to 0.

- When S= 1 and R= 0, the latch is set to 1.

- When S= 1 and R= 1, the output of both gates will produce 0.

i.e.,

$$Q_{n+1} = Q_{n+1}' = 0$$

.

| S | R | Qn | Q <sub>n+1</sub> | State         |

|---|---|----|------------------|---------------|

| 0 | 0 | 0  | 0                | No Change     |

| 0 | 0 | 1  | 1                | (NC)          |

| 0 | 1 | 0  | 0                | Reset         |

| 0 | 1 | 1  | 0                | Reset         |

| 1 | 0 | 0  | 1                | Set           |

| 1 | 0 | 1  | 1                | Jet           |

| 1 | 1 | 0  | х                | Indeterminate |

| 1 | 1 | 1  | х                | *             |

The truth table of NOR based SR latch is shown below.

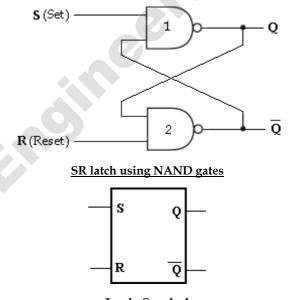

# SR latch using NAND gates:

The SR latch can also be implemented using NAND gates. The inputs of this Latch are S and R. To understand how this circuit functions, recall that a low on any input to a NAND gate forces its output high.

Logic Symbol

We can summarize the operation of SR latch as follows:

• When S= 0 and R= 0, the output of both gates will produce 0.

i.e.,  $Q_{n+1}=Q_{n+1}'=1$ .

- When S= 0 and R= 1, the latch is reset to 0.

- When S= 1 and R= 0, the latch is set to 1.

- When S=1 and R=1, the output,  $Q_{n+1}$  remains in its present state,  $Q_n$ .

| S | R | Qn | Q <sub>n+1</sub> | State         |

|---|---|----|------------------|---------------|

| 0 | 0 | 0  | х                | Indeterminate |

| 0 | 0 | 1  | x                | *             |

| 0 | 1 | 0  | 1                | Set           |

| 0 | 1 | 1  | 1                | 500           |

| 1 | 0 | 0  | 0                | Reset         |

| 1 | 0 | 1  | 0                | neset         |

| 1 | 1 | 0  | 0                | No Change     |

| 1 | 1 | 1  | 1                | (NC)          |

The truth table of NAND based SR latch is shown below.

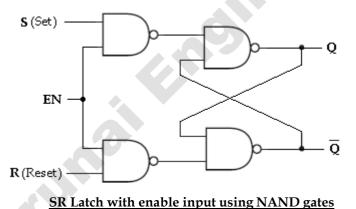

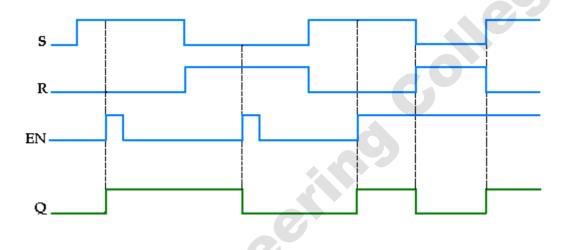

#### Gated SR Latch:

In the SR latch, the output changes occur immediately after the input changes i.e, the latch is sensitive to its S and R inputs all the time.

A latch that is sensitive to the inputs only when an enable input is active. Such a latch with enable input is known as gated SR latch.

• The circuit behaves like SR latch when EN= 1. It retains its previous state when EN= 0

<u>Logic Symbol</u>

The truth table of gated SR latch is show below.

| EN | S | R | Qn | Q <sub>n+1</sub> | State          |

|----|---|---|----|------------------|----------------|

| 1  | 0 | 0 | 0  | 0                | No Change (NC) |

| 1  | 0 | 0 | 1  | 1                | no change (nc) |

| 1  | 0 | 1 | 0  | 0                | Reset          |

| 1  | 0 | 1 | 1  | 0                | Neset          |

| 1 | 1 | 0 | 0 | 1 | Cat            |

|---|---|---|---|---|----------------|

| 1 | 1 | 0 | 1 | 1 | Set            |

| 1 | 1 | 1 | 0 | х | Indeterminate  |

| 1 | 1 | 1 | 1 | x | *              |

| 0 | x | х | 0 | 0 | No Change (NC) |

| 0 | х | х | 1 | 1 | No Change (NC) |

When S is HIGH and R is LOW, a HIGH on the EN input sets the latch. When S is LOW and R is HIGH, a HIGH on the EN input resets the latch.

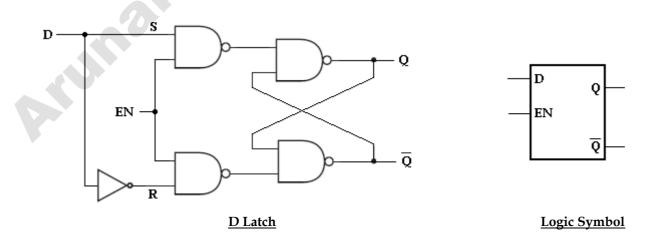

# 3.3.2 D Latch

In SR latch, when both inputs are same (00 or 11), the output either does not change or it is invalid. In many practical applications, these input conditions are not required. These input conditions can be avoided by making them complement of each other. This modified SR latch is known as **D latch**.

As shown in the figure, D input goes directly to the S input, and its complement is applied to the R input. Therefore, only two input conditions exists, either S=0 and R=1 or S=1 and R=0. The truth table for D latch is shown below.

| EN | D | Qn | Q <sub>n+1</sub> | State          |

|----|---|----|------------------|----------------|

| 1  | 0 | х  | 0                | Reset          |

| 1  | 1 | x  | 1                | Set            |

| 0  | x | х  | Qn               | No Change (NC) |

As shown in the truth table, the Q output follows the D input. For this reason, D latch is called *transparent latch*.

When D is HIGH and EN is HIGH. Q goes HIGH. When D is LOW and EN is HIGH, Q goes LOW. When EN is LOW, the state of the latch is not affected by the D input.

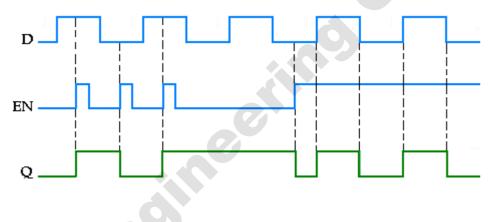

# <u>3.4</u> TRIGGERING OF FLIP-FLOPS

The state of a Flip-Flop is switched by a momentary change in the input signal. This momentary change is called a trigger and the transition it causes is said to trigger the Flip-Flop. Clocked Flip-Flops are triggered by pulses. A clock pulse starts from an initial value of 0, goes momentarily to 1 and after a short time, returns to its initial 0 value.

Latches are controlled by enable signal, and they are level triggered, either positive level triggered or negative level triggered. The output is free to change according to the S and R input values, when active level is maintained at the enable input. Flip-Flops are different from latches. Flip-Flops are pulse or clock edge triggered instead of level triggered.

# 3.5 EDGE TRIGGERED FLIP-FLOPS

Flip-Flops are synchronous bistable devices (has two outputs Q and Q'). In this case, the term synchronous means that the output changes state only at a specified point on the triggering input called the clock (CLK), i.e., changes in the output occur in synchronization with the clock.

An *edge-triggered Flip-Flop* changes state either at the positive edge (rising edge) or at the negative edge (falling edge) of the clock pulse and is sensitive to its inputs only at this transition of the clock. The different types of edge-triggered Flip-Flops are –

- S-R Flip-Flop,

- J-K Flip-Flop,

- D Flip-Flop,

- T Flip-Flop.

Although the S-R Flip-Flop is not available in IC form, it is the basis for the D and J-K Flip-Flops. Each type can be either positive edge-triggered (no bubble at C

input) or negative edge-triggered (bubble at C input). The key to identifying an edge- triggered Flip-Flop by its logic symbol is the small triangle inside the block at the clock (C) input. This triangle is called the **dynamic input indicator**.

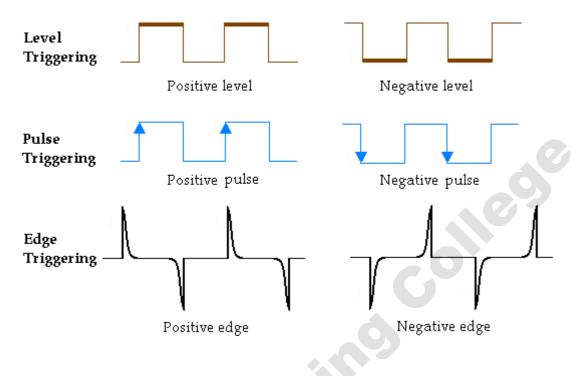

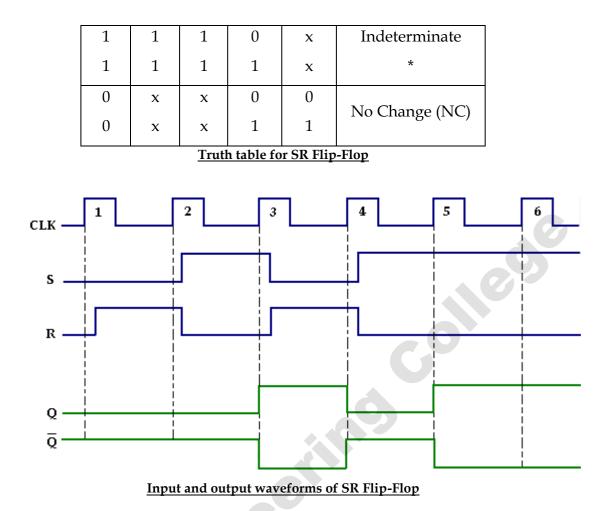

#### 3.5.1 S-R Flip-Flop

The S and R inputs of the S-R Flip-Flop are called *synchronous* inputs because data on these inputs are transferred to the Flip-Flop's output only on the triggering edge of the clock pulse. The circuit is similar to SR latch except enable signal is replaced by clock pulse (CLK). On the positive edge of the clock pulse, the circuit responds to the S and R inputs.

When S is HIGH and R is LOW, the Q output goes HIGH on the triggering edge of the clock pulse, and the Flip-Flop is SET. When S is LOW and R is HIGH, the Q output goes LOW on the triggering edge of the clock pulse, and the Flip-Flop is RESET. When both S and R are LOW, the output does not change from its prior state. An invalid condition exists when both S and R are HIGH.

| CLK | S | R | Qn | Q <sub>n+1</sub> | State          |

|-----|---|---|----|------------------|----------------|

| 1   | 0 | 0 | 0  | 0                | No Change (NC) |

| 1   | 0 | 0 | 1  | 1                | No Change (NC) |

| 1   | 0 | 1 | 0  | 0                | Reset          |

| 1   | 0 | 1 | 1  | 0                | Reset          |

| 1   | 1 | 0 | 0  | 1                | Set            |

| 1   | 1 | 0 | 1  | 1                | Jet            |

# 3.5.2 J-K Flip-Flop:

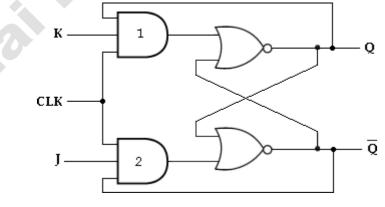

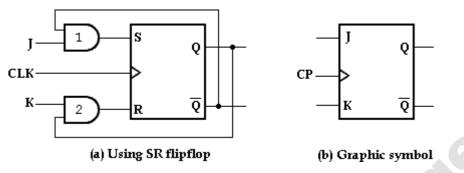

JK means Jack Kilby, Texas Instrument (TI) Engineer, who invented IC in 1958. JK Flip-Flop has two inputs J(set) and K(reset). A JK Flip-Flop can be obtained from the clocked SR Flip-Flop by augmenting two AND gates as shown below.

<u>JK Flip Flop</u>

The data input J and the output Q' are applied o the first AND gate and its output (JQ') is applied to the S input of SR Flip-Flop. Similarly, the data input K and

the output Q are applied to the second AND gate and its output (KQ) is applied to the R input of SR Flip-Flop.

J= K= 0

When J=K= 0, both AND gates are disabled. Therefore clock pulse have no effect, hence the Flip-Flop output is same as the previous output.

J= 0, K= 1

When J= 0 and K= 1, AND gate 1 is disabled i.e., S= 0 and R= 1. This condition will reset the Flip-Flop to 0.

J=1, K=0

When J= 1 and K= 0, AND gate 2 is disabled i.e., S= 1 and R= 0. Therefore the Flip-Flop will set on the application of a clock pulse.

J= K= 0

When J=K= 1, it is possible to set or reset the Flip-Flop. If Q is High, AND gate 2 passes on a reset pulse to the next clock. When Q is low, AND gate 1 passes on a set pulse to the next clock. Eitherway, Q changes to the complement of the last state i.e., toggle. Toggle means to switch to the opposite state.

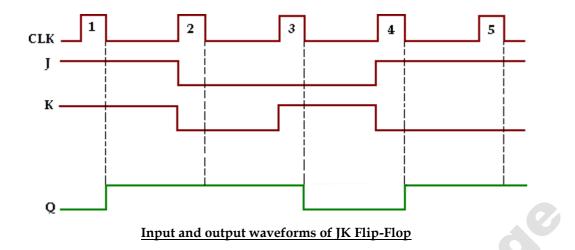

The truth table of JK Flip-Flop is given below.

| 7 | CLK | Inp | outs | Output           | State     |

|---|-----|-----|------|------------------|-----------|

|   | CLK | J   | K    | Q <sub>n+1</sub> | State     |

|   | 1   | 0   | 0    | Qn               | No Change |

|   | 1   | 0   | 1    | 0                | Reset     |

|   | 1   | 1   | 0    | 1                | Set       |

|   | 1   | 1   | 1    | Q <sub>n</sub> ' | Toggle    |

# Characteristic table and Characteristic equation:

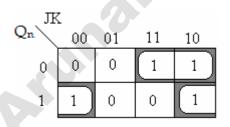

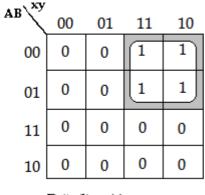

The characteristic table for JK Flip-Flop is shown in the table below. From the table, K-map for the next state transition  $(Q_{n+1})$  can be drawn and the simplified logic expression which represents the characteristic equation of JK Flip-Flop can be found.

| Qn | J      | K           | Q <sub>n+1</sub> |

|----|--------|-------------|------------------|

| 0  | 0      | 0           | 0                |

| 0  | 0      | 1           | 0                |

| 0  | 1      | 0           | 1                |

| 0  | 1      | 1           | 1                |

| 1  | 0      | 0           | 1                |

| 1  | 0      | 1           | 0                |

| 1  | 1      | 0           | 1                |

| 1  | 1      | 1           | 0                |

|    | Charac | teristic ta | ble              |

K-map Simplification:

Characteristic equation:  $Q_{n+1} = JQ' + K'Q$ .

# 3.5.3 D Flip-Flop:

Arun

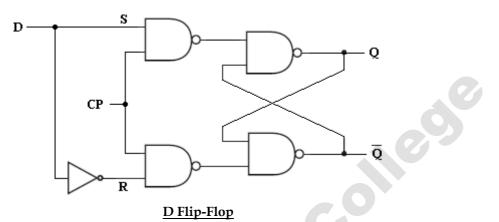

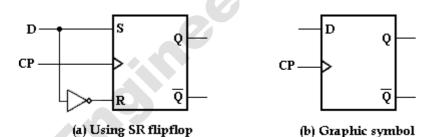

Like in D latch, in D Flip-Flop the basic SR Flip-Flop is used with complemented inputs. The D Flip-Flop is similar to D-latch except clock pulse is used instead of enable input.

To eliminate the undesirable condition of the indeterminate state in the RS Flip-Flop is to ensure that inputs S and R are never equal to 1 at the same time. This is done by D Flip-Flop. The D (*delay*) Flip-Flop has one input called delay input and clock pulse input. The D Flip-Flop using SR Flip-Flop is shown below.

The truth table of D Flip-Flop is given below.

| Clock | D      | Q <sub>n+1</sub> | State       |

|-------|--------|------------------|-------------|

| 1     | 0      | 0                | Reset       |

| 1     | 1      | 1                | Set         |

| 0     | х      | Qn               | No Change   |

|       | Taurth | table for        | D Flin Flon |

Truth table for D Flip-Flop

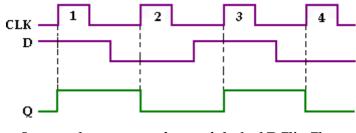

Input and output waveforms of clocked D Flip-Flop

Looking at the truth table for D Flip-Flop we can realize that  $Q_{n+1}$  function follows the D input at the positive going edges of the clock pulses.

#### Characteristic table and Characteristic equation:

The characteristic table for D Flip-Flop shows that the next state of the Flip-Flop is independent of the present state since  $Q_{n+1}$  is equal to D. This means that an input pulse will transfer the value of input D into the output of the Flip-Flop independent of the value of the output before the pulse was applied.

The characteristic equation is derived from K-map.

Characteristic equation:  $Q_{n+1} = D$ .

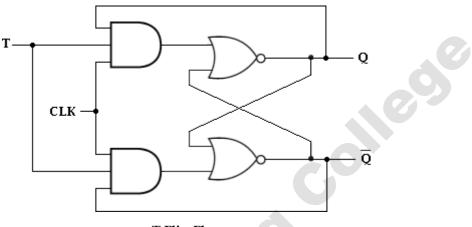

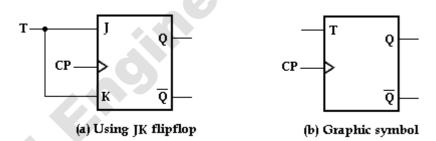

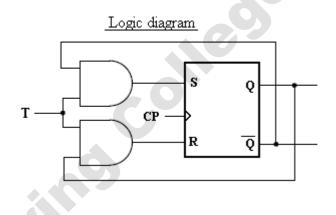

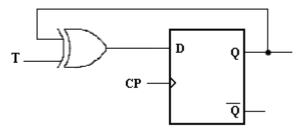

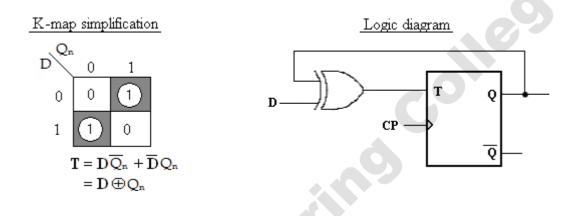

# 3.5.4 T Flip-Flop

The T (Toggle) Flip-Flop is a modification of the JK Flip-Flop. It is obtained from JK Flip-Flop by connecting both inputs J and K together, i.e., single input. Regardless of the present state, the Flip-Flop complements its output when the clock pulse occurs while input T= 1.

<u>T Flip-Flop</u>

When T=0,  $Q_{n+1}=Q_n$ , i.e., the next state is the same as the present state and no change occurs.

When T= 1,  $Q_{n+1} = Q_n'$ , i.e., the next state is the complement of the present state.

The truth table of T Flip-Flop is given below.

| Т      | Q <sub>n+1</sub>            | State     |  |  |  |

|--------|-----------------------------|-----------|--|--|--|

| 0      | Qn                          | No Change |  |  |  |

| 1      | Q <sub>n</sub> ′            | Toggle    |  |  |  |

|        |                             |           |  |  |  |

| ,<br>, | Truth table for T Flip-Flop |           |  |  |  |

<u>uth table for 1 Flip-Flop</u>

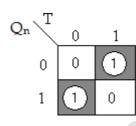

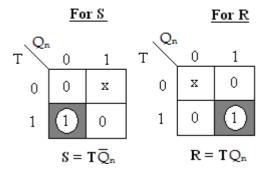

#### Characteristic table and Characteristic equation:

The characteristic table for T Flip-Flop is shown below and characteristic equation is derived using K-map.

| Qn | Т | Q <sub>n+1</sub> |

|----|---|------------------|

| 0  | 0 | 0                |

| 0  | 1 | 1                |

| 1  | 0 | 1                |

| 1  | 1 | 0                |

K-map Simplification:

olleg

Characteristic equation:  $Q_{n+1} = TQ_n' + T'Q_n$ .

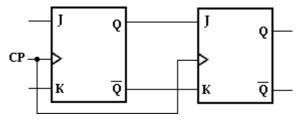

#### 3.5.5 Master-Slave JK Flip-Flop

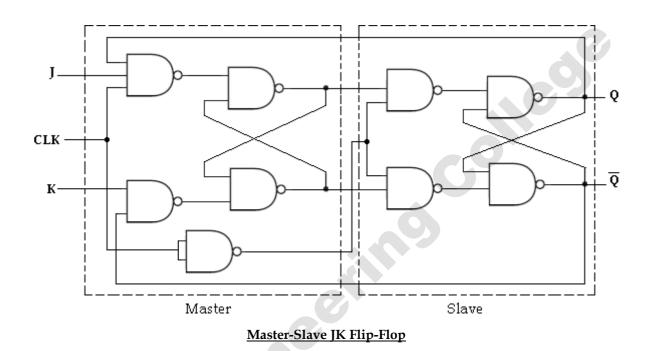

A master-slave Flip-Flop is constructed using two separate JK Flip-Flops. The first Flip-Flop is called the master. It is driven by the positive edge of the clock pulse. The second Flip-Flop is called the slave. It is driven by the negative edge of the clock pulse. The logic diagram of a master-slave JK Flip-Flop is shown below.

#### <u>Logic diagram</u>

When the clock pulse has a positive edge, the master acts according to its J-K inputs, but the slave does not respond, since it requires a negative edge at the clock input.

When the clock input has a negative edge, the slave Flip-Flop copies the master outputs. But the master does not respond since it requires a positive edge at its clock input.

The clocked master-slave J-K Flip-Flop using NAND gates is shown below.

# **<u>3.6</u>** APPLICATION TABLE (OR) EXCITATION TABLE:

The *characteristic table* is useful for **analysis** and for defining the operation of the Flip-Flop. It specifies the next state  $(Q_{n+1})$  when the inputs and present state are known.

The *excitation or application table* is useful for **design** process. It is used to find the Flip-Flop input conditions that will cause the required transition, when the present state  $(Q_n)$  and the next state  $(Q_{n+1})$  are known.

3.6.1 SR Flip-Flop:

| Present<br>State | Inputs |   | Next<br>State    |

|------------------|--------|---|------------------|

| Qn               | S      | R | Q <sub>n+1</sub> |

| 0                | 0      | 0 | 0                |

| 0                | 0      | 1 | 0                |

| 0                | 1      | 0 | 1                |

| 0                | 1      | 1 | x                |

| 1                | 0      | 0 | 1                |

| 1                | 0      | 1 | 0                |

| 1                | 1      | 0 | 1                |

| 1                | 1      | 1 | x                |

| Present<br>State | Next<br>State    | Inputs |   | Inp | outs |

|------------------|------------------|--------|---|-----|------|

| Qn               | Q <sub>n+1</sub> | S      | R | S   | R    |

| 0                | 0                | 0      | 0 | 0   | x    |

| 0                | 0                | 0      | 1 | Ŭ   |      |

| 0                | 1                | 1      | 0 | 1   | 0    |

| 1                | 0                | 0      | 1 | 0   | 1    |

| 1                | 1                | 0      | 0 | x   | 0    |

| 1                | 1                | 1      | 0 |     | 5    |

Modified Table

#### Characteristic Table

| Present  | Next             | Inputs |   |  |  |  |

|----------|------------------|--------|---|--|--|--|

| State    | State            |        |   |  |  |  |

| Qn       | Q <sub>n+1</sub> | S      | R |  |  |  |

| 0        | 0                | 0      | x |  |  |  |

| 0        | 1                | 1      | 0 |  |  |  |

| 1        | 0                | 0      | 1 |  |  |  |

| 1        | 1                | x      | 0 |  |  |  |

| <u>E</u> | Excitation Table |        |   |  |  |  |

The above table presents the excitation table for SR Flip-Flop. It consists of present state  $(Q_n)$ , next state  $(Q_{n+1})$  and a column for each input to show how the required transition is achieved.

There are 4 possible transitions from present state to next state. The required Input conditions for each of the four transitions are derived from the information available in the characteristic table. The symbol 'x' denotes the don't care condition, it does not matter whether the input is 0 or 1.

# 3.6.2 JK Flip-Flop:

| Present<br>State | Inputs |   | Next<br>State |

|------------------|--------|---|---------------|

| Qn               | J      | K | Qn+1          |

| 0                | 0      | 0 | 0             |

| 0                | 0      | 1 | 0             |

| 0                | 1      | 0 | 1             |

| 0                | 1      | 1 | 1             |

| 1                | 0      | 0 | 1             |

| 1                | 0      | 1 | 0             |

| 1                | 1      | 0 | 1             |

| 1                | 1      | 1 | 0             |

| Present<br>State | Next<br>State    | Inputs |   | Inp | outs |

|------------------|------------------|--------|---|-----|------|

| Qn               | Q <sub>n+1</sub> | J      | K | J   | К    |

| 0                | 0                | 0      | 0 | 0   | x    |

| 0                | 0                | 0      | 1 | 0   | λ    |

| 0                | 1                | 1      | 0 | 1   | x    |

| 0                | 1                | 1      | 1 |     |      |

| 1                | 0                | 0      | 1 | x   | 1    |

| 1                | 0                | 1      | 1 | ~   | L    |

| 1                | 1                | 0      | 0 | x   | 0    |

| 1                | 1                | 1      | 0 | Λ   | Ū    |

# Characteristic Table

# Modified Table

| Present Next |                |     |      |

|--------------|----------------|-----|------|

| State        | State          | Inp | outs |

| Qn           | Qn+1           | J   | K    |

| 0            | 0              | 0   | х    |

| 0            | 1              | 1   | x    |

| 1            | 0              | x   | 1    |

| 1            | 1              | x   | 0    |

| <u> </u>     | xcitation Tabl | e   |      |

|              |                |     |      |

|              |                |     |      |

|              |                |     |      |

|              |                |     |      |

|              |                |     |      |

# 3.6.3 D Flip-Flop

| Present | Innut | Next             |

|---------|-------|------------------|

| State   | Input | State            |

| Qn      | D     | Q <sub>n+1</sub> |

| 0       | 0     | 0                |

| 0       | 1     | 1                |

| 1       | 0     | 0                |

| 1       | 1     | 1                |

Characteristic Table

#### Present Next Input State State D $Q_{n+1}$ Qn 0 0 0 0 1 1 0 1 0 1 1 1

Excitation Table

# 3.6.4 T Flip-Flop

| Present<br>State | Input | Next<br>State    |  |

|------------------|-------|------------------|--|

| Qn               | Т     | Q <sub>n+1</sub> |  |

| 0                | 0     | 0                |  |

| 0                | 1     | 1                |  |

| 1                | 0     | 1                |  |

| 1                | 1     | 0                |  |

Characteristic Table

| Present<br>State | Next<br>State    | Input |

|------------------|------------------|-------|

| Qn               | Q <sub>n+1</sub> | Т     |

| 0                | 0                | 0     |

| 0                | 1                | 1     |

| 1                | 0                | 1     |

| 1                | 1                | 0     |

Modified Table

# 3.7 REALIZATION OF ONE FLIP-FLOP USING OTHER FLIP-FLOPS

It is possible to convert one Flip-Flop into another Flip-Flop with some additional gates or simply doing some extra connection. The realization of one Flip-Flop using other Flip-Flops is implemented by the use of characteristic tables and excitation tables. Let us see few conversions among Flip-Flops.

olleg

- ★ SR Flip-Flop to D Flip-Flop

- ★ SR Flip-Flop to JK Flip-Flop

- ✤ SR Flip-Flop to T Flip-Flop

- ✗ JK Flip-Flop to T Flip-Flop

- ✤ JK Flip-Flop to D Flip-Flop

- ✤ D Flip-Flop to T Flip-Flop

- ★ T Flip-Flop to D Flip-Flop

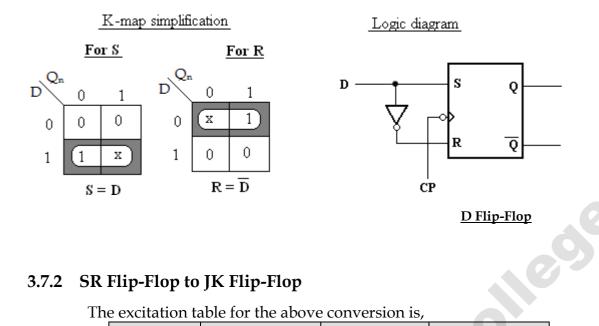

# 3.7.1 SR Flip-Flop to D Flip-Flop:

- Write the characteristic table for required Flip-Flop (D Flip-Flop).

- Write the excitation table for given Flip-Flop (SR Flip-Flop).

- Determine the expression for the given Flip-Flop inputs (S and R) by using K- map.

- Draw the Flip-Flop conversion logic diagram to obtain the required Flip-Flop (D Flip-Flop) by using the above obtained expression.

The excitation table for the above conversion is

| Required Flip-Flop (D)         |    |                  | Given Fl<br>(SI |        |

|--------------------------------|----|------------------|-----------------|--------|

| Input Present state Next state |    |                  | Flip-Flop       | Inputs |

| D                              | Qn | Q <sub>n+1</sub> | S               | R      |

| 0                              | 0  | 0                | 0               | x      |

| 0                              | 1  | 0                | 0               | 1      |

| 1                              | 0  | 1                | 1               | 0      |

| 1                              | 1  | 1                | x               | 0      |

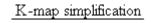

#### 3.7.2 SR Flip-Flop to JK Flip-Flop

The excitation table for the above conversion is,

| Inp | outs | Present state | Next state       | Flip-<br>Inj | -Flop<br>put |

|-----|------|---------------|------------------|--------------|--------------|

| J   | Κ    | Qn            | Q <sub>n+1</sub> | S            | R            |

| 0   | 0    | 0             | 0                | 0            | x            |

| 0   | 0    | 1             | 1                | x            | 0            |

| 0   | 1    | 0             | 0                | 0            | x            |

| 0   | 1    | 1             | 0                | 0            | 1            |

| 1   | 0    | 0             | 1                | 1            | 0            |

| 1   | 0    | 1             | 1                | x            | 0            |

| 1   | 1    | 0             | 1                | 1            | 0            |

| 1   | 1    | 1             | 0                | 0            | 1            |

K-map simplification

# 2.7.3 SR Flip-Flop to T Flip-Flop

| Input | Present state | Next state       | Flip<br>Inj | -Flop<br>puts |

|-------|---------------|------------------|-------------|---------------|

| Т     | Qn            | Q <sub>n+1</sub> | Qn+1 S      |               |

| 0     | 0             | 0 0 0            |             | x             |

| 0     | 1             | 1                | х           | 0             |

| 1     | 0             | 1                | 1           | 0             |

| 1     | 1             | 0                | 0           | 1             |

The excitation table for the above conversion is

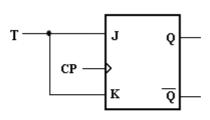

# 3.7.4 JK Flip-Flop to T Flip-Flop

The excitation table for the above conversion is

| Input | Present state | Next state       | Flip<br>Inj | -Flop<br>outs |

|-------|---------------|------------------|-------------|---------------|

| Т     | Qn            | Q <sub>n+1</sub> | J           | K             |

| 0     | 0             | 0                | 0           | х             |

| 0     | 1             | 1                | х           | 0             |

| 1     | 0             | 1                | 1           | x             |

| 1     | 1             | 0                | х           | 1             |

K-map simplification

1

х

х

J = T

| T | 0 | 1 |

|---|---|---|

| 0 | x | 0 |

| 1 | x | 1 |

For K

K = T

Logic diagram

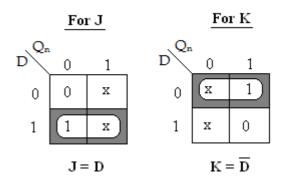

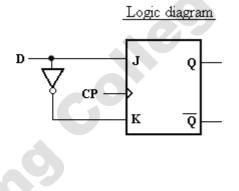

# JK Flip-Flop to D Flip-Flop

| Input | Present state | Next state       | Flip<br>Inj | -Flop<br>puts |

|-------|---------------|------------------|-------------|---------------|

| D     | Qn            | Q <sub>n+1</sub> | J           | K             |

| 0     | 0             | 0                | 0           | х             |

| 0     | 1 0           |                  | х           | 1             |

| 1     | 0             | 1                | 1           | x             |

| 1     | 1             | 1                | х           | 0             |

The excitation table for the above conversion is

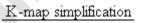

# D Flip-Flop to T Flip-Flop

The excitation table for the above conversion is

| Input | Present state | Next state       | Flip-Flop<br>Input |

|-------|---------------|------------------|--------------------|

| Т     | Qn            | Q <sub>n+1</sub> | D                  |

| 0     | 0             | 0                | 0                  |

| 0     | 1             | 1                | 1                  |

| 1     | 0             | 1                | 1                  |

| 1     | 1             | 0                | 0                  |

| NU.   |               |                  |                    |

# **T Flip-Flop to D Flip-Flop**

| Input | ut Present state Next state |                  | Flip-Flop<br>Input |

|-------|-----------------------------|------------------|--------------------|

| D     | Qn                          | Q <sub>n+1</sub> | Т                  |

| 0     | 0                           | 0                | 0                  |

| 0     | 1                           | 0                | 1                  |

| 1     | 0                           | 1                | 1                  |

| 1     | 1                           | 1                | 0                  |

The excitation table for the above conversion is

# 3.8 CLASSIFICATION OF SYNCHRONOUS SEQUENTIAL CIRCUIT:

In synchronous or clocked sequential circuits, clocked Flip-Flops are used as memory elements, which change their individual states in synchronism with the periodic clock signal. Therefore, the change in states of Flip-Flop and change in state of the entire circuits occur at the transition of the clock signal.

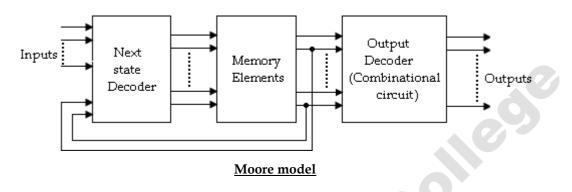

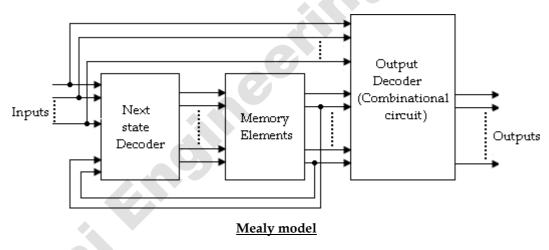

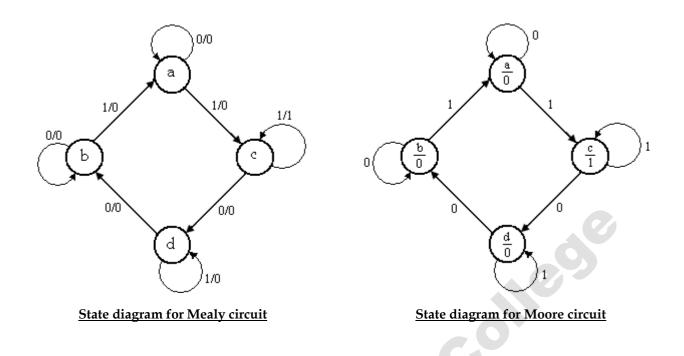

The synchronous or clocked sequential networks are represented by two models.

- Moore model: The output depends only on the present state of the Flip-Flops.

- **Mealy model:** The output depends on both the present state of the Flip-Flops and on the inputs.

# 3.8.1 Moore model:

In the Moore model, the outputs are a function of the present state of the Flip-Flops only. The output depends only on present state of Flip-Flops, it appears only after the clock pulse is applied, i.e., it varies in synchronism with the clock input.

# 3.8.2 Mealy model:

In the Mealy model, the outputs are functions of both the present state of the Flip-Flops and inputs.

# 3.8.3 Difference between Moore and Mealy model

| S1.No | Moore model                         | Mealy model                               |

|-------|-------------------------------------|-------------------------------------------|

| 1     | Its output is a function of present | Its output is a function of present state |

|       | state only.                         | as well as present input.                 |

| 2     | Input changes does not affect the   | Input changes may affect the output of    |

|       | output.                             | the circuit.                              |

| 3     | It requires more number of states   | It requires less number of states for     |

|       | for implementing same function.     | implementing same function.               |

# 3.9 ANALYSIS OF SYNCHRONOUS SEQUENTIAL CIRCUIT:

The behavior of a sequential circuit is determined from the inputs, outputs and the state of its Flip-Flops. The outputs and the next state are both a function of the inputs and the present state. The analysis of a sequential circuit consists of obtaining a table or diagram from the time sequence of inputs, outputs and internal states.

Before going to see the analysis and design examples, we first understand the state diagram, state table.

#### 3.9.1 State Diagram

# State diagram is a pictorial representation of a behavior of a sequential circuit.

- In the state diagram, a state is represented by a circle and the transition between states is indicated by directed lines connecting the circles.

- A directed line connecting a circle with circle with itself indicates that next state is same as present state.

- The binary number inside each circle identifies the state represented by the circle.

- The directed lines are labeled with two binary numbers separated by a symbol '/'. The input value that causes the state transition is labeled first and the output value during the present state is labeled after the symbol '/'.

In case of Moore circuit, the directed lines are labeled with only one binary number representing the state of the input that causes the state transition. The output state is indicated within the circle, below the present state because output state depends only on present state and not on the input.

# 3.9.2 State Table

# State table represents relationship between input, output and Flip-Flop states.

- It consists of three sections labeled present state, next state and output.

- The present state designates the state of Flip-Flops before the occurrence of a clock pulse, and the output section gives the values of the output variables during the present state.

- Both the next state and output sections have two columns representing two possible input conditions: X= 0 and X=1.

| Present state | Next state |      | Output |      |

|---------------|------------|------|--------|------|

|               | X= 0       | X= 1 | X= 0   | X= 1 |

| AB            | AB         | AB   | Y      | Y    |

| a             | а          | С    | 0      | 0    |

| b             | b          | а    | 0      | 0    |

| С             | d          | С    | 0      | 1    |

| d             | b          | d    | 0      | 0    |

In case of Moore circuit, the output section has only one column since output does not depend on input.

| Present state | Next | Output |   |

|---------------|------|--------|---|

|               | X= 0 | X= 1   | Y |

| AB            | AB   | AB     |   |

| a             | а    | С      | 0 |

| b             | b    | а      | 0 |

| С             | d    | С      | 1 |

| d             | b    | d      | 0 |

# 2.9.3 State Equation

It is an algebraic expression that specifies the condition for a Flip-Flop state transition.

The Flip-Flops may be of any type and the logic diagram may or may not include combinational circuit gates.

# 3.9.4 ANALYSIS PROCEDURE

The synchronous sequential circuit analysis is summarizes as given below:

- 1. Assign a state variable to each Flip-Flop in the synchronous sequential circuit.

- 2. Write the excitation input functions for each Flip-Flop and also write the Moore/ Mealy output equations.

- 3. Substitute the excitation input functions into the bistable equations for the Flip-Flops to obtain the next state output equations.

- 4. Obtain the state table and reduced form of the state table.

- 5. Draw the state diagram by using the second form of the state table.

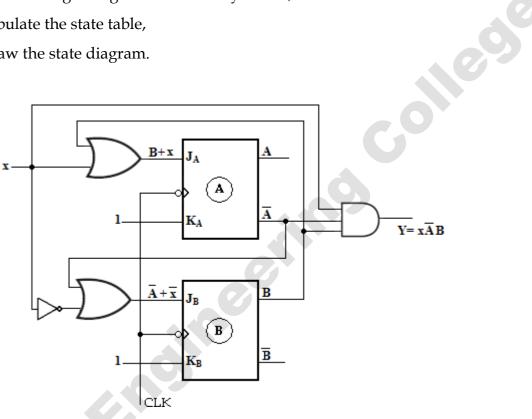

# 3.9.5 Analysis of Mealy Model

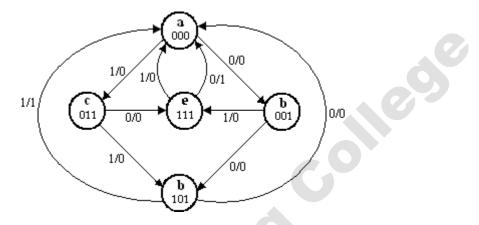

- 1. A sequential circuit has two JK Flip-Flops A and B, one input (x) and one output

- (y). the Flip-Flop input functions are,

$$J_A = B + x$$

$J_B = A' + x'$

$K_A = 1$   $K_B = 1$

and the circuit output function, **Y= xA**'**B**.

- a) Draw the logic diagram of the Mealy circuit,

- b) Tabulate the state table,

- c) Draw the state diagram.

# Soln:

#### State table:

To obtain the next-state values of a sequential circuit with JK Flip-Flops, use the JK Flip-Flop characteristics table.

| Prese | nt state | Input | Input Flip-Flop Inputs Next sta |                   | state                                                 | Output    |        |        |         |

|-------|----------|-------|---------------------------------|-------------------|-------------------------------------------------------|-----------|--------|--------|---------|

| Α     | В        | x     | $J_A = B + x$                   | K <sub>A</sub> =1 | $\mathbf{J}_{\mathrm{B}} = \mathbf{A'} + \mathbf{x'}$ | $K_B = 1$ | A(t+1) | B(t+1) | Y= xA'B |

| 0     | 0        | 0     | 0                               | 1                 | 1                                                     | 1         | 0      | 1      | 0       |

| 0     | 0        | 1     | 1                               | 1                 | 1                                                     | 1         | 1      | 1      | 0       |

| 0     | 1        | 0     | 1                               | 1                 | 1                                                     | 1         | 1      | 0      | 0       |

| 0     | 1        | 1     | 1                               | 1                 | 1                                                     | 1         | 1      | 0      | 1       |

| 1     | 0        | 0     | 0                               | 1                 | 1                                                     | 1         | 0      | 1      | 0       |

| 1     | 0        | 1     | 1                               | 1                 | 0                                                     | 1         | 0      | 0      | 0       |

| 1     | 1        | 0     | 1                               | 1                 | 1                                                     | 1         | 0      | 0      | 0       |

| 1     | 1        | 1     | 1                               | 1                 | 0                                                     | 1         | 0      | 0      | 0       |

| Present state<br>x= 0 |   | Next state |   |      |      | Output |   |

|-----------------------|---|------------|---|------|------|--------|---|

|                       |   | x= 1       |   | x= 0 | x= 1 |        |   |

| Α                     | В | Α          | В | Α    | В    | у      | у |

| 0                     | 0 | 0          | 1 | 1    | 1    | 0      | 0 |

| 0                     | 1 | 1          | 0 | 1    | 0    | 0      | 1 |

| 1                     | 0 | 0          | 1 | 0    | 0    | 0      | 0 |

| 1                     | 1 | 0          | 0 | 0    | 0    | 0      | 0 |

Second form of state table

legi

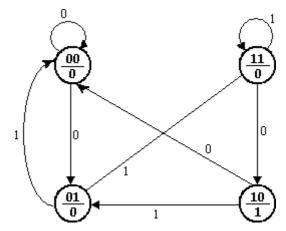

# State Diagram:

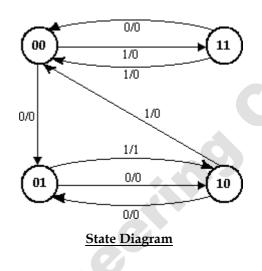

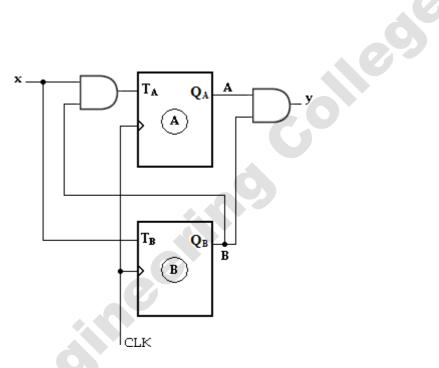

2. A sequential circuit with two 'D' Flip-Flops A and B, one input (x) and one output (y). the Flip-Flop input functions are:

$D_A = Ax + Bx$

$D_B = A'x$  and the circuit output function is,

Y=(A+B) x'.

- (a) Draw the logic diagram of the circuit,

- (b) Tabulate the state table,

- (c) Draw the state diagram.

# Soln:

| Present state |   | Input | Flip-Flop Inputs          |             | Next state |        | Output     |

|---------------|---|-------|---------------------------|-------------|------------|--------|------------|

| Α             | В | x     | D <sub>A</sub> =<br>Ax+Bx | $D_B = A'x$ | A(t+1)     | B(t+1) | Y= (A+B)x' |

| 0             | 0 | 0     | 0                         | 0           | 0          | 0      | 0          |

| 0             | 0 | 1     | 0                         | 1           | 0          | 1      | 0          |

| 0             | 1 | 0     | 0                         | 0           | 0          | 0      | 1          |

| 0             | 1 | 1     | 1                         | 1           | 1          | 1      | 0          |

| 1             | 0 | 0     | 0                         | 0           | 0          | 0      | 1          |

| 1             | 0 | 1     | 1                         | 0           | 1          | 0      | 0          |

| 1             | 1 | 0     | 0                         | 0           | 0          | 0      | 1          |

| 1             | 1 | 1     | 1                         | 0           | 1          | 0      | 0          |

|   | 1                          | 1     | 1             | 1 |            | 0 | 1    | 0 | 0      |  |

|---|----------------------------|-------|---------------|---|------------|---|------|---|--------|--|

| _ |                            |       | 0             |   |            |   |      |   |        |  |

|   |                            | T     | Present state |   | Next state |   |      |   | Output |  |

| P |                            | Prese |               |   | x= 0       |   | x= 1 |   | x= 1   |  |

|   |                            | Α     | В             | Α | В          | Α | В    | Y | Y      |  |

|   |                            | 0     | 0             | 0 | 0          | 0 | 1    | 0 | 0      |  |

|   |                            | 0     | 1             | 0 | 0          | 1 | 1    | 1 | 0      |  |

|   |                            | 1     | 0             | 0 | 0          | 1 | 0    | 1 | 0      |  |

|   |                            | 1     | 1             | 0 | 0          | 1 | 0    | 1 | 0      |  |

|   | Second form of state table |       |               |   |            |   |      |   |        |  |

Second form of state table

State Diagram:

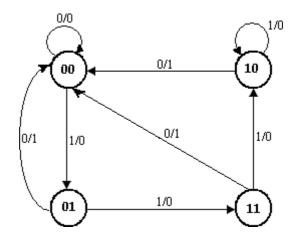

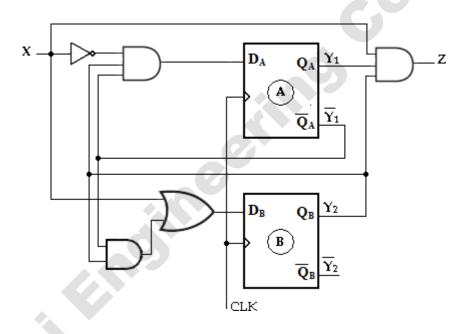

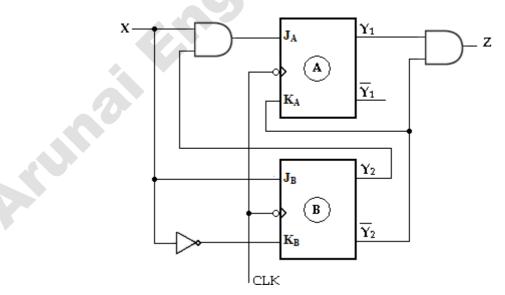

3. Analyze the synchronous Mealy machine and obtain its state diagram.

# Soln:

The given synchronous Mealy machine consists of two D Flip-Flops, one inputs and one output.

The Flip-Flop input functions are,

$$D_{A} = Y_{1}'Y_{2}X'$$

$$D_{B} = X + Y_{1}'Y_{2}$$

The circuit output function is,  $Z=Y_1Y_2X$

State Table:

| Present state  |                       | Input | Flip-Flo            | Next state          |                      | Output               |             |  |

|----------------|-----------------------|-------|---------------------|---------------------|----------------------|----------------------|-------------|--|

| Y <sub>1</sub> | <b>Y</b> <sub>2</sub> | X     | $D_A = Y_1' Y_2 X'$ | $D_B = X + Y_1'Y_2$ | Y <sub>1</sub> (t+1) | Y <sub>2</sub> (t+1) | $Z=Y_1Y_2X$ |  |

| 0              | 0                     | 0     | 0                   | 0                   | 0                    | 0                    | 0           |  |

| 0              | 0                     | 1     | 0                   | 1                   | 0                    | 1                    | 0           |  |

| 0              | 1                     | 0     | 1                   | 1                   | 1                    | 1                    | 0           |  |

| 0              | 1                     | 1     | 0                   | 1                   | 0                    | 1                    | 0           |  |

| 1              | 0                     | 0     | 0                   | 0                   | 0                    | 0                    | 0           |  |

| 1              | 0                     | 1     | 0                   | 1                   | 0                    | 1                    | 0           |  |

| 1              | 1                     | 0     | 0                   | 0                   | 0                    | 0                    | 0           |  |

| 1              | 1                     | 1     | 0                   | 1                   | 0                    | 1                    | 1           |  |

|                |                       |       |                     |                     |                      |                      |             |  |

| Present state  |                |                       | Nex            | Output         |                |     |      |

|----------------|----------------|-----------------------|----------------|----------------|----------------|-----|------|

|                |                | X= 0                  |                | X= 1           |                | X=0 | X= 1 |

| Y <sub>1</sub> | Y <sub>2</sub> | <b>Y</b> <sub>1</sub> | Y <sub>2</sub> | Y <sub>1</sub> | Y <sub>2</sub> | Z   | Z    |

| 0              | 0              | 0                     | 0              | 0              | 1              | 0   | 0    |

| 0              | 1              | 1                     | 1              | 0              | 1              | 0   | 0    |

| 1              | 0              | 0                     | 0              | 0              | 1              | 0   | 0    |

| 1              | 1              | 0                     | 0              | 0              | 1              | 0   | 1    |

Second form of state table

# State Diagram:

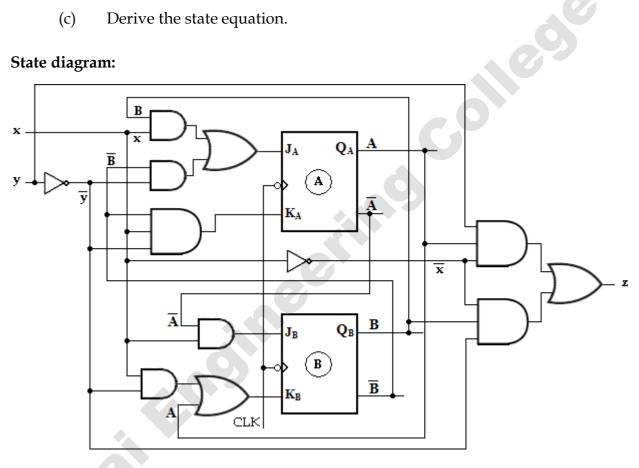

A sequential circuit has two JK Flop-Flops A and B, two inputs x and y and 4. one output z. The Flip-Flop input equation and circuit output equations are

$$J_A = Bx + B' y'$$

$K_A = B' xy'$

$J_B = A' x$   $K_B = A + xy'$

$z = Ax' y' + Bx' y'$

- Draw the logic diagram of the circuit (a)

- (b) Tabulate the state table.

- (c) Derive the state equation.

## State diagram:

### State table:

To obtain the next-state values of a sequential circuit with JK Flip-Flop, use the JK Flip-Flop characteristic table,

|   | esent<br>ate | Inp | out |                             | Flip-Flop                 | Inputs          |                           | Next   | state  | Output |

|---|--------------|-----|-----|-----------------------------|---------------------------|-----------------|---------------------------|--------|--------|--------|

| Α | В            | x   | у   | J <sub>A</sub> =<br>Bx+B'y' | K <sub>A</sub> =<br>B'xy' | $J_{B} =$ $A'x$ | K <sub>B</sub> =<br>A+xy' | A(t+1) | B(t+1) | Z      |

| 0 | 0            | 0   | 0   | 1                           | 0                         | 0               | 0                         | 1      | 0      | 0      |

| 0 | 0            | 0   | 1   | 0                           | 0                         | 0               | 0                         | 0      | 0      | 0      |

| 0 | 0            | 1   | 0   | 1                           | 1                         | 1               | 1                         | 1      | 1      | 0      |

| 0 | 0            | 1   | 1   | 0                           | 0                         | 1               | 0                         | 0      | 1      | 0      |

| 0 | 1            | 0   | 0   | 0                           | 0                         | 0               | 0                         | 0      | 0      | 1      |

| 0 | 1            | 0   | 1   | 0                           | 0                         | 0               | 0                         | 0      | 0      | 0      |

| 0 | 1            | 1   | 0   | 1                           | 0                         | 1               | 1                         | 1      | 1      | 0      |

| 0 | 1            | 1   | 1   | 1                           | 0                         | 1               | 0                         | 1      | 1      | 0      |

| 1 | 0            | 0   | 0   | 1                           | 0                         | 0               | 1                         | 1      | 0      | 1      |

| 1 | 0            | 0   | 1   | 0                           | 0                         | 0               | 1                         | 1      | 0      | 0      |

| 1 | 0            | 1   | 0   | 1                           | 1                         | 0               | 1                         | 0      | 0      | 0      |

| 1 | 0            | 1   | 1   | 0                           | 0                         | 0               | 1                         | 1      | 0      | 0      |

| 1 | 1            | 0   | 0   | 0                           | 0                         | 0               | 1                         | 1      | 0      | 1      |

| 1 | 1            | 0   | 1   | 0                           | 0                         | 0               | 1                         | 1      | 0      | 0      |

| 1 | 1            | 1   | 0   | 1                           | 0                         | 0               | 1                         | 1      | 0      | 0      |

| 1 | 1            | 1   | 1   | 1                           | 0                         | 0               | 1                         | 1      | 0      | 0      |

# State Equation:

| For A(t+1) |         |     |       |       |        |  |

|------------|---------|-----|-------|-------|--------|--|

| AB XY      | 00      | 01  | 11    | 10    |        |  |

| 00         | 1       | 0   | 0     | 1     |        |  |

| 01         | 0       | 0   | 1     | 1     |        |  |

| 11         | 1       | 1   | 1     | 1     |        |  |

| 10         | 1       |     | 1     | 0     |        |  |

| A          | A (t+1) | =Ax | + Ay+ | Bx+ A | A'B'y' |  |

$\mathbf{B}\left(\mathbf{t+1}\right)=\mathbf{A'x}$

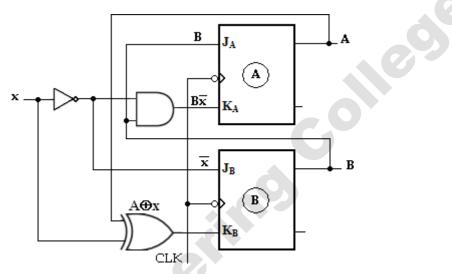

- 5. A sequential circuit has two JK Flip-Flop A and B. the Flip-Flop input functions

- are:  $J_A = B$   $J_B = x'$  $K_A = Bx'$   $K_B = A \oplus x$ .

- (a) Draw the logic diagram of the circuit,

- (b) Tabulate the state table,

- (c) Draw the state diagram.

## Logic diagram:

The output function is not given in the problem. The output of the Flip-Flops may be considered as the output of the circuit.

## State table:

To obtain the next-state values of a sequential circuit with JK Flip-Flop, use the JK Flip-Flop characteristic table.

| Pres | ent state | Input |                    | Flip-Flo             | op Inputs  |             | Next   | state  |

|------|-----------|-------|--------------------|----------------------|------------|-------------|--------|--------|

| Α    | В         | x     | J <sub>A</sub> = B | K <sub>A</sub> = Bx' | $J_B = x'$ | $K_B = A x$ | A(t+1) | B(t+1) |

| 0    | 0         | 0     | 0                  | 0                    | 1          | 0           | 0      | 1      |

| 0    | 0         | 1     | 0                  | 0                    | 0          | 1           | 0      | 0      |

| 0    | 1         | 0     | 1                  | 1                    | 1          | 0           | 1      | 1      |

| 0    | 1         | 1     | 1                  | 0                    | 0          | 1           | 1      | 0      |

| 1    | 0         | 0     | 0                  | 0                    | 1          | 1           | 1      | 1      |

| 1    | 0         | 1     | 0                  | 0                    | 0          | 0           | 1      | 0      |

| 1    | 1         | 0     | 1                  | 1                    | 1          | 1           | 0      | 0      |

| 1    | 1         | 1     | 1                  | 0                    | 0          | 0           | 1      | 1      |

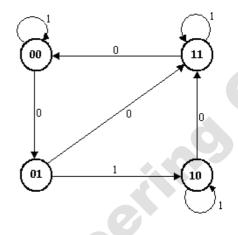

| D      |          |            | Nex        | X=1         A       B         0       0         1       0         1       0         1       1         table       1 |     |  |

|--------|----------|------------|------------|---------------------------------------------------------------------------------------------------------------------|-----|--|

| Presei | nt state | X=         | = 0        | X=                                                                                                                  | = 1 |  |

| Α      | В        | Α          | В          | Α                                                                                                                   | В   |  |

| 0      | 0        | 0          | 1          | 0                                                                                                                   | 0   |  |

| 0      | 1        | 1          | 1          | 1                                                                                                                   | 0   |  |

| 1      | 0        | 1          | 1          | 1                                                                                                                   | 0   |  |

| 1      | 1        | 0          | 0          | 1                                                                                                                   | 1   |  |

|        | 5        | Second for | m of state | table                                                                                                               |     |  |

|        |          |            |            |                                                                                                                     |     |  |

|        | $\cap$   | .1<br>)    |            | $\bigcap^{1}$                                                                                                       |     |  |

|        | 6        | •)₊        | 0          |                                                                                                                     |     |  |

State Diagram:

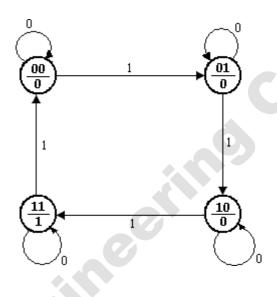

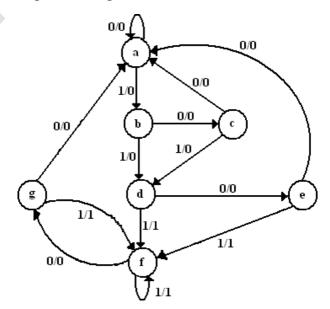

## 3.9.6 Analysis of Moore Model

6. Analyze the synchronous Moore circuit and obtain its state diagram.

## Soln:

Using the assigned variable Y<sub>1</sub> and Y<sub>2</sub> for the two JK Flip-Flops, we can write the four excitation input equations and the Moore output equation as follows:

| $J_A = Y_2 X$ | ; | $K_A = Y_2'$ |

|---------------|---|--------------|

| $J_B = X$     | ; | $K_B = X'$   |

and output function,  $Z = Y_1 Y_2'$

| State ( | able:    |       |               |                                   |           |            |          |                      |             |

|---------|----------|-------|---------------|-----------------------------------|-----------|------------|----------|----------------------|-------------|

| Preser  | nt state | Input |               | Flip-Flop Inputs Next sta         |           |            | state    | Output               |             |

| Y1      | $Y_2$    | X     | $J_A = Y_2 X$ | K <sub>A</sub> = Y <sub>2</sub> ' | $J_B = X$ | $K_B = X'$ | Y1 (t+1) | Y <sub>2</sub> (t+1) | $Z=Y_1Y_2'$ |

| 0       | 0        | 0     | 0             | 1                                 | 0         | 1          | 0        | 0                    | 0           |

| 0       | 0        | 1     | 0             | 1                                 | 1         | 0          | 0        | 1                    | 0           |

| 0       | 1        | 0     | 0             | 0                                 | 0         | 1          | 0        | 0                    | 0           |

| 0       | 1        | 1     | 1             | 0                                 | 1         | 0          | 1        | 1                    | 0           |

| 1       | 0        | 0     | 0             | 1                                 | 0         | 1          | 0        | 0                    | 1           |

| 1       | 0        | 1     | 0             | 1                                 | 1         | 0          | 0        | 1                    | 1           |

| 1       | 1        | 0     | 0             | 0                                 | 0         | 1          | 1        | 0                    | 0           |

| 1       | 1        | 1     | 1             | 0                                 | 1         | 0          | 1        | 1                    | 0           |

| D              |                       |                       | Output         |              |                |   |

|----------------|-----------------------|-----------------------|----------------|--------------|----------------|---|

| Presei         | nt state              | X=                    | = 0            | X= 1         |                | N |

| Y <sub>1</sub> | <b>Y</b> <sub>2</sub> | <b>Y</b> <sub>1</sub> | Y <sub>2</sub> | Y1           | Y <sub>2</sub> | Ĩ |

| 0              | 0                     | 0                     | 0              | 0            | 1              | 0 |

| 0              | 1                     | 0                     | 0              | 1            | 1              | 0 |

| 1              | 0                     | 0                     | 0              | 0            | 1              | 1 |

| 1              | 1                     | 1                     | 0              | 1            | 1              | 0 |

|                |                       | Seco                  | nd form o      | f state tabl | e              |   |

## State Diagram:

Aru

Here the output depends on the present state only and is independent of the input. The two values inside each circle separated by a slash are for the present state and output.

7. A sequential circuit has two T Flip-Flop A and B. The Flip-Flop input functions are:

$$T_{A}=Bx T_{B}=x$$

y= AB

- (a) Draw the logic diagram of the circuit,

- (b) Tabulate the state table,

- (c) Draw the state diagram.

## Soln:

Logic diagram:

## State table

| Pres | ent state | Input | Flip-Flo   | p Inputs  | Next    | state   | Output |

|------|-----------|-------|------------|-----------|---------|---------|--------|

| Α    | В         | x     | $T_A = Bx$ | $T_B = x$ | A (t+1) | B (t+1) | y= AB  |

| 0    | 0         | 0     | 0          | 0         | 0       | 0       | 0      |

| 0    | 0         | 1     | 0          | 1         | 0       | 1       | 0      |

| 0    | 1         | 0     | 0          | 0         | 0       | 1       | 0      |

| 0    | 1         | 1     | 1          | 1         | 1       | 0       | 0      |

| 1    | 0         | 0     | 0          | 0         | 1       | 0       | 0      |

| 1    | 0         | 1     | 0          | 1         | 1       | 1       | 0      |

| 1    | 1         | 0     | 0          | 0         | 1       | 1       | 1      |

| 1    | 1         | 1     | 1          | 1         | 0       | 0       | 1      |

| Present state |          |    | Nex | Output |   |      |      |

|---------------|----------|----|-----|--------|---|------|------|

| Presei        | nt state | x= | = 0 | x= 1   |   | x= 0 | x= 1 |

| Α             | В        | Α  | В   | Α      | В | у    | у    |

| 0             | 0        | 0  | 0   | 0      | 1 | 0    | 0    |

| 0             | 1        | 0  | 1   | 1      | 0 | 0    | 0    |

| 1             | 0        | 1  | 0   | 1      | 1 | 0    | 0    |

| 1             | 1        | 1  | 1   | 0      | 0 | 1    | 1    |

Second form of state table

10

State Diagram:

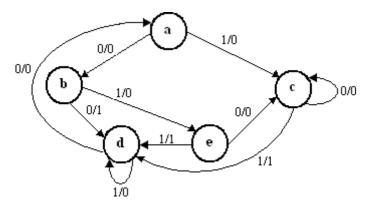

## 3.10 STATE REDUCTION/ MINIMIZATION

The state reduction is used to avoid the redundant states in the sequential circuits. The reduction in redundant states reduces the number of required Flip-Flops and logic gates, reducing the cost of the final circuit.

The two states are said to be redundant or equivalent, if every possible set of inputs generate exactly same output and same next state. When two states are equivalent, one of them can be removed without altering the input-output relationship.

Since 'n' Flip-Flops produced 2<sup>n</sup> state, a reduction in the number of states may result in a reduction in the number of Flip-Flops.

The need for state reduction or state minimization is explained with one example.

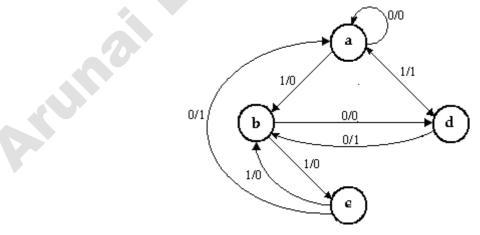

State diagram

| Step 1: Determine | the state table for | or given state diagram |

|-------------------|---------------------|------------------------|

| otep it Determine | the state table it  | Si given state angiani |

| Present state | Next  | state | Output |      |  |

|---------------|-------|-------|--------|------|--|

| Tresent state | X= 0  | X= 1  | X= 0   | X= 1 |  |

| a             | b     | С     | 0      | 0    |  |

| b             | d     | е     | 1      | 0    |  |

| С             | С     | d     | 0      | 1    |  |

| d             | a     | d     | 0      | 0    |  |

| e             | С     | d     | 0      | 1    |  |

|               | State | table | •      |      |  |

## **Step 2: Find equivalent states**

Dr

From the above state table **c** and **e** generate exactly same next state and same output for every possible set of inputs. The state **c** and **e** go to next states **c** and **d** and have outputs 0 and 1 for x=0 and x=1 respectively. Therefore state **e** can be removed and replaced by **c**. The final reduced state table is shown below.

| Present state | Next      | state      | Output |      |  |

|---------------|-----------|------------|--------|------|--|

| Tresent state | X= 0      | X= 1       | X= 0   | X= 1 |  |

| a             | b         | С          | 0      | 0    |  |

| b             | d         | С          | 1      | 0    |  |

| С             | С         | d          | 0      | 1    |  |

| d             | а         | d          | 0      | 0    |  |

|               | Reduced s | tate table |        |      |  |

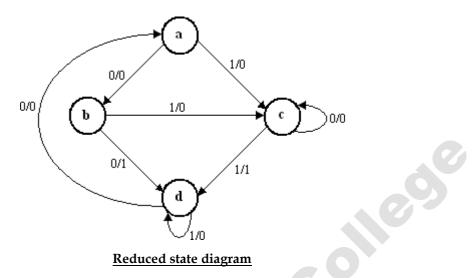

The state diagram for the reduced table consists of only four states and is shown below.

1. Reduce the number of states in the following state table and tabulate the reduced state table.

| Present state  | Next | state | Out  | put  |

|----------------|------|-------|------|------|

| i resent state | X= 0 | X= 1  | X= 0 | X= 1 |

| a              | а    | b     | 0    | 0    |

| b              | С    | d     | 0    | 0    |

| С              | a    | d     | 0    | 0    |

| d              | e    | f     | 0    | 1    |

| е              | а    | f     | 0    | 1    |

| f              | g    | f     | 0    | 1    |

| g              | а    | f     | 0    | 1    |

## Soln:

From the above state table **e** and **g** generate exactly same next state and same output for every possible set of inputs. The state **e** and **g** go to next states **a** and **f** and have outputs 0 and 1 for x=0 and x=1 respectively. Therefore state **g** can be removed and replaced by **e**.

The reduced state table-1 is shown below.

| Present state | Next | state | Out  | put  |

|---------------|------|-------|------|------|

|               | X= 0 | X= 1  | X= 0 | X= 1 |

| a             | а    | b     | 0    | 0    |

| b             | С    | d     | 0    | 0    |

| С             | а    | d     | 0    | 0    |

| d             | e    | f     | 0    | 1    |

| e             | а    | f     | 0    | 1    |

| f             | е    | f     | 0    | 1    |

#### Reduced state table-1

Now states d and f are equivalent. Both states go to the same next state (e, f) and have same output (0, 1). Therefore one state can be removed; **f** is replaced by **d**. The final reduced state table-2 is shown below.

| Present state | Next state |      | Output |      |

|---------------|------------|------|--------|------|

| riesent state | X= 0       | X= 1 | X= 0   | X= 1 |

| а             | а          | b    | 0      | 0    |

| b             | С          | d    | 0      | 0    |

| С             | a          | d    | 0      | 0    |

| d             | e          | d    | 0      | 1    |

| е             | a          | d    | 0      | 1    |

Reduced state table-2

Thus 7 states are reduced into 5 states.

2. Determine a minimal state table equivalent furnished below

| Present state | Next | state |

|---------------|------|-------|

| Tresent state | X= 0 | X=1   |

| 1             | 1,0  | 1,0   |

| 2             | 1, 1 | 6, 1  |

| 3             | 4,0  | 5,0   |

| 4             | 1, 1 | 7,0   |

| 5             | 2, 0 | 3, 0  |

| 6             | 4,0  | 5,0   |

| 7             | 2, 0 | 3, 0  |

| Present state | Next | state | Out  | put  |

|---------------|------|-------|------|------|

| riesent state | X= 0 | X= 1  | X= 0 | X= 1 |

| 1             | 1    | 1     | 0    | 0    |

| 2             | 1    | 6     | 1    | 1    |

| 3             | 4    | 5     | 0    | 0    |

| 4             | 1    | 7     | 1    | 0    |

| 5             | 2    | 3     | 0    | 0    |

| 6             | 4    | 5     | 0    | 0    |

| 7             | 2    | 3     | 0    | 0    |

|               |      |       |      |      |

From the above state table, **5** and **7** generate exactly same next state and same output for every possible set of inputs. The state **5** and **7** go to next states **2** and **3** and have outputs 0 and 0 for x=0 and x=1 respectively. Therefore state **7** can be removed and replaced by **5**.

Similarly, **3** and **6** generate exactly same next state and same output for every possible set of inputs. The state **3** and **6** go to next states **4** and **5** and have outputs 0 and 0 for x=0 and x=1 respectively. Therefore state **6** can be removed and replaced by **3**.

|   | Present state | Next      | Next state |      | Output |  |

|---|---------------|-----------|------------|------|--------|--|

|   | Tresent state | X= 0      | X= 1       | X= 0 | X= 1   |  |

| 9 | 1             | 1         | 1          | 0    | 0      |  |

|   | 2             | 1         | 3          | 1    | 1      |  |

|   | 3             | 4         | 5          | 0    | 0      |  |

|   | 4             | 1         | 5          | 1    | 0      |  |

|   | 5             | 2         | 3          | 0    | 0      |  |

|   | <u>.</u>      | Reduced s | tate table |      |        |  |

The final reduced state table is shown below.

Thus 7 states are reduced into 5 states.

Soln:

| Present state | Next state |      |  |

|---------------|------------|------|--|

|               | X= 0       | X=1  |  |

| А             | D, 0       | C, 1 |  |

| В             | E, 1       | A, 1 |  |

| С             | H, 1       | D, 1 |  |

| D             | D, 0       | C, 1 |  |

| Е             | В, 0       | G, 1 |  |

| F             | H, 1       | D, 1 |  |

| G             | A, 0       | F, 1 |  |

| Н             | C, 0       | A, 1 |  |

| Ι             | G, 1       | H,1  |  |

Soln:

| -             |      | _, .  | -/ - |      |   |

|---------------|------|-------|------|------|---|

| ]             | E    | B, 0  | G, 1 |      |   |

| ]             | F    | H, 1  | D, 1 |      |   |

| (             | G    | A, 0  | F, 1 |      |   |

| I             | Н    | C, 0  | A, 1 |      |   |

|               | Ι    | G, 1  | H,1  |      |   |

|               |      |       |      |      |   |

|               |      |       |      |      |   |

| Present state | Next | state | Out  | put  |   |

|               | X= 0 | X= 1  | X= 0 | X= 1 |   |

| А             | D    | C     | 0    | 1    |   |

| В             | E    | A     | 1    | 1    |   |

| С             | H    | D     | 1    | 1    |   |

| D             | D    | C     | 0    | 1    |   |

| Е             | В    | G     | 0    | 1    |   |

| F             | Н    | D     | 1    | 1    |   |

| G             | A    | F     | 0    | 1    |   |

| Н             | C    | А     | 0    | 1    |   |

| Ι             | G    | Н     | 1    | 1    |   |

|               |      |       |      |      | • |

From the above state table, **A** and **D** generate exactly same next state and same output for every possible set of inputs. The state **A** and **D** go to next states **D** and **C** and have outputs 0 and 1 for x=0 and x=1 respectively. Therefore state **D** can be removed and replaced by **A**. Similarly, **C** and **F** generate exactly same next state and same output for every possible set of inputs. The state **C** and **F** go to next states **H** and **D** and have outputs 1 and 1 for x=0 and x=1 respectively. Therefore state **F** can be removed and replaced by **C**.

The reduced state table-1 is shown below.

3. Minimize the following state table.

| Present state | Next       | Next state  |      | put  |

|---------------|------------|-------------|------|------|

| Tresent state | X= 0       | X= 1        | X= 0 | X= 1 |

| А             | А          | C           | 0    | 1    |

| В             | Е          | А           | 1    | 1    |

| С             | Η          | А           | 1    | 1    |

| Е             | В          | G           | 0    | 1    |

| G             | А          | С           | 0    | 1    |

| Н             | С          | А           | 0    | 1    |

| Ι             | G          | Н           | 1    | 1    |

|               | Reduced st | ate table-1 |      | •    |

From the above reduced state table-1, **A** and **G** generate exactly same next state and same output for every possible set of inputs. The state **A** and **G** go to next states **A** and **C** and have outputs 0 and 1 for x=0 and x=1 respectively. Therefore state **G** can be removed and replaced by **A**. The final reduced state table-2 is shown below.

| Present state | Next state |      | Output |      |

|---------------|------------|------|--------|------|

| Tresent state | X= 0       | X= 1 | X= 0   | X= 1 |

| А             | А          | С    | 0      | 1    |

| В             | Е          | Α    | 1      | 1    |

| С             | Н          | A    | 1      | 1    |

| Е             | В          | А    | 0      | 1    |

| Н             | C          | А    | 0      | 1    |

| Ι             | A          | Η    | 1      | 1    |

Reduced state table-2

Thus 9 states are reduced into 6 states.

4. Reduce the following state diagram.

Arui

| Present state | Next state   |       | Output |      |

|---------------|--------------|-------|--------|------|

| Tresent state | X= 0         | X= 1  | X= 0   | X= 1 |

| а             | а            | b     | 0      | 0    |

| b             | С            | d     | 0      | 0    |

| С             | а            | d     | 0      | 0    |

| d             | e            | f     | 0      | 1    |

| е             | а            | f     | 0      | 1    |

| f             | g            | f     | 0      | 1    |

| g             | а            | f     | 0      | 1    |

|               | <u>State</u> | table |        |      |

From the above state table **e** and **g** generate exactly same next state and same output for every possible set of inputs. The state **e** and **g** go to next states **a** and **f** and have outputs 0 and 1 for x=0 and x=1 respectively. Therefore state **g** can be removed and replaced by **e**. The reduced state table-1 is shown below.

| Present state | Next | Next state |      | put  |

|---------------|------|------------|------|------|

|               | X= 0 | X= 1       | X= 0 | X= 1 |

| a             | а    | b          | 0    | 0    |

| b             | С    | d          | 0    | 0    |

| С             | a    | d          | 0    | 0    |

| d             | e    | f          | 0    | 1    |

| e             | a    | f          | 0    | 1    |

| f             | e    | f          | 0    | 1    |

### Reduced state table-1

Now states d and f are equivalent. Both states go to the same next state (e, f) and have same output (0, 1). Therefore one state can be removed; **f** is replaced by **d**. The final reduced state table-2 is shown below.

| Present state | Next       | state       | Output |      |  |

|---------------|------------|-------------|--------|------|--|

|               | X= 0       | X= 1        | X= 0   | X= 1 |  |

| a             | a          | b           | 0      | 0    |  |

| b             | С          | d           | 0      | 0    |  |

| С             | a          | d           | 0      | 0    |  |

| d             | e          | d           | 0      | 1    |  |

| e             | а          | d           | 0      | 1    |  |

|               | Reduced st | ate table-2 |        |      |  |

Thus 7 states are reduced into 5 states.

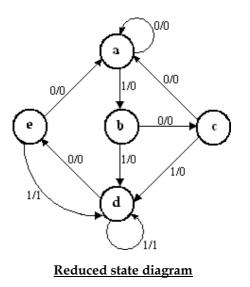

The state diagram for the reduced state table-2 is,

## Soln:

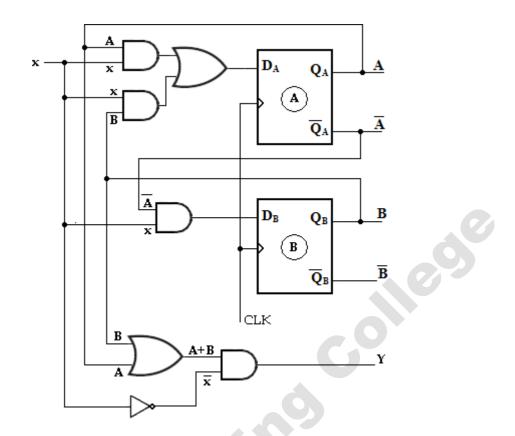

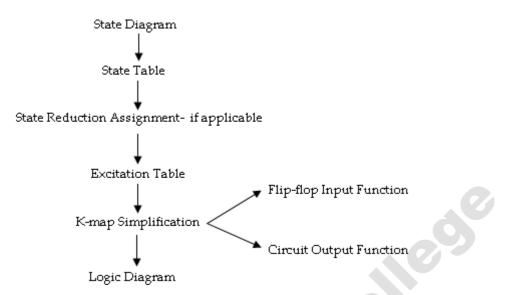

## 3.11 DESIGN OF SYNCHRONOUS SEQUENTIAL CIRCUITS:

A synchronous sequential circuit is made up of number of Flip-Flops and combinational gates. The design of circuit consists of choosing the Flip-Flops and then finding a combinational gate structure together with the Flip-Flops. The number of Flip-Flops is determined from the number of states needed in the circuit. The combinational circuit is derived from the state table.

## 3.11.1 Design procedure:

- 1. The given problem is determined with a state diagram.

- 2. From the state diagram, obtain the state table.

- 3. The number of states may be reduced by state reduction methods (if applicable).

- 4. Assign binary values to each state (Binary Assignment) if the state table contains letter symbols.

- 5. Determine the number of Flip-Flops and assign a letter symbol (A, B, C,...) to each.

- 6. Choose the type of Flip-Flop (SR, JK, D, T) to be used.

- 7. From the state table, circuit excitation and output tables.

- 8. Using K-map or any other simplification method, derive the circuit output functions and the Flip-Flop input functions.

- 9. Draw the logic diagram.

The type of Flip-Flop to be used may be included in the design specifications or may depend what is available to the designer. Many digital systems are constructed with JK Flip-Flops because they are the most versatile available. The selection of inputs is given as follows.

| Flip-Flop | Application                        |

|-----------|------------------------------------|

| JK        | General Applications               |

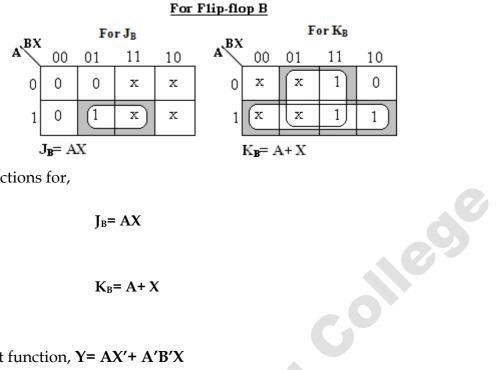

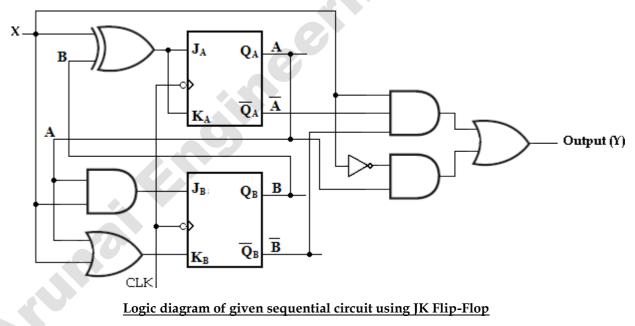

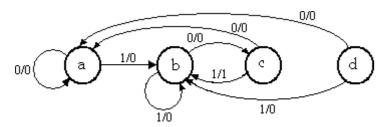

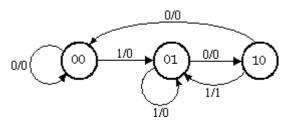

| D         | Applications requiring transfer of |